# Lecture Notes in Computer Science

3637

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

J. Manuel Moreno Jordi Madrenas Jordi Cosp (Eds.)

# Evolvable Systems: From Biology to Hardware

6th International Conference, ICES 2005 Sitges, Spain, September 12-14, 2005 Proceedings

#### Volume Editors

J. Manuel Moreno

Jordi Madrenas

Jordi Cosp

Technical University of Catalunya

Department of Electronic Engineering

Campus Nord, Building C4, c/Jordi Girona 1-3

08034 Barcelona, Spain

E-mail: {moreno,madrenas,jcosp}@eel.upc.edu

Library of Congress Control Number: 2005931797

CR Subject Classification (1998): B.6, B.7, F.1, I.6, I.2, J.2, J.3

ISSN 0302-9743

ISBN-10 3-540-28736-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-28736-0 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11549703 06/3142 5 4 3 2 1 0

# **Preface**

The flying machines proposed by Leonardo da Vinci in the fifteenth century, the self-reproducing automata theory proposed by John von Neumann in the middle of the twentieth century and the current possibility of designing electronic and mechanical systems using evolutionary principles are all examples of the efforts made by humans to explore the mechanisms present in biological systems that permit them to tackle complex tasks. These initiatives have recently given rise to the emergent field of bioinspired systems and evolvable hardware. The inaugural workshop, Towards Evolvable Hardware, took place in Lausanne in October 1995, followed by the successive events of the International Conference on Evolvable Systems: From Biology to Hardware, held in Tsukuba (Japan) in October 1996, in Lausanne (Switzerland) in September 1998, in Edinburgh (UK) in April 2000, in Tokyo (Japan) in October 2001, and in Trondheim (Norway) in March 2003.

Following the success of these past events the sixth international conference was aimed at presenting the latest developments in the field, bringing together researchers who use biologically inspired concepts to implement real systems in artificial intelligence, artificial life, robotics, VLSI design, and related domains. The sixth conference consolidated this biennial event as a reference meeting for the community involved in bio-inspired systems research.

All the papers received were reviewed by at least three independent reviewers, thus guaranteeing a high-quality bundle for ICES 2005. The conference included three keynote talks entitled: "Perspectives in Complex Systems Research", "Neural Coding of Auditory Information" and "Evolutionary Approaches to Articulated Robot Locomotion". The conference program consisted of 21 technical presentations and a panel debate. Additionally, a varied social program was set up to foster the exchange of ideas in an enjoyable environment.

We would like to thank the reviewers for their time and effort in reviewing all of the submitted papers. We would also like to thank the other members of the Organizing Committee. We wish to thank the following for their direct support of this conference: the Technical University of Catalunya (UPC), the Department of Electronics of the Technical University of Catalunya, the Spanish Ministry of Education, Culture and Sports, the Funding Agency for Universities and Research of the Generalitat de Catalunya (AGAUR), and Xilinx, Inc. Last, but not least, we would like to thank all the authors who invested so much time and effort in their research work and decided to join us in making ICES 2005 a successful event.

And what is to come next? It is not so easy to make forecasts in a research field that is moving as fast as ours about findings and understanding relating to the basic mechanisms that underlie the living forms we can observe. Of course, technology will play a major role in allowing for an actual realization of these principles, and this is where nanotechnology and new FPGA architectures will provide the necessary

substrate. However, in our opinion it will be the close cooperation between bioscientists, mathematicians and engineers that will result in a framework able to permit the construction of artifacts with emergent properties similar to those we can see even in the simplest living being. For sure in the next ICES conference we will see most of the topics that we have covered in the past, including evolving hardware design (both digital and analogue); evolutionary hardware design methodologies; self-repairing hardware; self-replicating hardware; embryonic hardware and self-developing systems; morphogenesis; neural hardware and adaptive hardware platforms; autonomous robots; evolutionary robotics; and molecular computation. As for the new topics that will emerge in this research field, it is our feeling that the breakthroughs coming in the life sciences in the coming years will provide avenues for facing challenges that, like consciousness, still constitute what Schopenhauer termed the world's knot.

We hope you enjoy reading these proceedings as much as we enjoyed putting them together.

September 2005

J. Manuel Moreno Jordi Madrenas Jordi Cosp

# **Organization**

# **Organizing Committee**

General Chair Juan Manuel Moreno Arostegui, Technical University

of Catalunya (UPC), Spain

Program Co-chair Gianluca Tempesti, Swiss Federal Institute of Technology,

Lausanne, Switzerland

Program Co-chair Joan Cabestany, Technical University of Catalunya

(UPC), Spain

Local Chair Jordi Madrenas, Technical University of Catalunya

(UPC), Spain

Publicity Chair Jordi Cosp, Technical University of Catalunya (UPC),

Spain

# **International Steering Committee**

Pauline C. Haddow, Norwegian University of Science and Technology, Norway Tetsuya Higuchi, Electrotechnical Laboratory, Japan Julian Miller, University of York, UK Jim Torresen, University of Oslo, Norway Andy Tyrrell, University of York, UK

# **Program Committee**

Wolfgang Banzhaf, University of Newfoundland, Canada

Peter Bentley, University College London, UK

Stefano Cagnoni, Universitá di Parma, Italy

Prabhas Chongstitvatana, Chulalongkorn University, Thailand

Carlos A. Coello, CINVESTAV-IPN, Mexico

Marco Dorigo, Université Libre de Bruxelles, Belgium

Rolf Drechsler, University of Bremen, Germany

Marc Ebner, Universität Würzburg, Germany

Stuart J. Flockton, Royal Holloway University of London, UK

Dario Floreano, Swiss Federal Institute of Technology, Lausanne, Switzerland

Andrew Greensted, University of York, UK

Tim Gordon, University College London, UK

Darko Grundler, Univesity of Zagreb, Croatia

Pauline C. Haddow, Norwegian University of Science and Technology, Norway

David M. Halliday, University of York, UK

Alister Hamilton, Edinburgh University, UK

Arturo Hernandez Aguirre, Tulane University, USA

Francisco Herrera, University of Granada, Spain

Tetsuya Higuchi, Electrotechnical Laboratory, Japan

Masaya Iwata, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Tatiana Kalganova, Brunel University, UK

Didier Keymeulen, Jet Propulsion Laboratory, USA

William B. Langdon, University College London, UK

Yong Liu, University of Aizu, Japan

Jason Lohn, NASA Ames Research Center, USA

Daniel Mange, Swiss Federal Institute of Technology, Lausanne, Switzerland

Karlheinz Meier, University of Heidelberg, Germany

Julian Miller, University of York, UK

David Montana, BBN Technologies, USA

Juan Manuel Moreno Arostegui, Technical University of Catalunya (UPC), Spain Masahiro Murakawa, National Institute of Advanced Industrial Science and

Technology (AIST), Japan

Eduardo Sanchez, Swiss Federal Institute of Technology, Lausanne, Switzerland

Lukas Sekanina, Brno University of Technology, Czech Republic

Moshe Sipper, Ben-Gurion University, Israel

Giovanni Squillero, Politecnico di Torino, Italy

André Stauffer, Swiss Federal Institute of Technology, Lausanne, Switzerland

Adrian Stoica, Jet Propulsion Lab, USA

Gianluca Tempesti, Swiss Federal Institute of Technology, Lausanne, Switzerland

Christof Teuscher, University of California, San Diego (UCSD), USA

Jon Timmis, University of Kent at Canterbury, UK

Adrian Thompson, University of Sussex, UK

Jim Torresen, University of Oslo, Norway

Gunnar Tufte, Norwegian University of Science and Technology, Norway

Andy Tyrrell, University of York, UK

Milan Vasilko, Bournemouth University, UK

Alessandro Villa, Université Joseph Fourier, Grenoble, France

Moritoshi Yasunaga, University of Tsukuba, Japan

Ricardo Zebulum, Jet Propulsion Lab, USA

# **Sponsoring Institutions**

We wish to thank the following for their contribution to the success of this conference:

Ministry of Education, Culture and Sports of Spain

Funding Agency for Universities and Research of the Generalitat de Catalunya (AGAUR)

Technical University of Catalunya (UPC)

Department of Electronics of the Technical University of Catalunya Xilinx, Inc.

# **Table of Contents**

| Fault Tolerance and Recovery                                                                                                                                    |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| An Adaptive Self-tolerant Algorithm for Hardware Immune System Wenjian Luo, Xin Wang, Ying Tan, Yiguo Zhang, Xufa Wang                                          | 1  |

| Consensus-Based Evaluation for Fault Isolation and On-line Evolutionary Regeneration  Kening Zhang, Ronald F. DeMara, Carthik A. Sharma                         | 12 |

| Hardware Fault-Tolerance Within the POEtic System  Will Barker, Andy M. Tyrrell                                                                                 | 25 |

| Evolvable Hardware System at Extreme Low Temperatures Ricardo S. Zebulum, Adrian Stoica, Didier Keymeulen, Lukas Sekanina, Rajeshuni Ramesham, Xin Guo          | 37 |

| Platforms for Evolving Digital Systems                                                                                                                          |    |

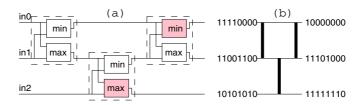

| Intrinsic Evolution of Sorting Networks: A Novel Complete Hardware Implementation for FPGAs  Jan Kořenek, Lukáš Sekanina                                        | 46 |

| Evolving Hardware by Dynamically Reconfiguring Xilinx FPGAs  Andres Upegui, Eduardo Sanchez                                                                     | 56 |

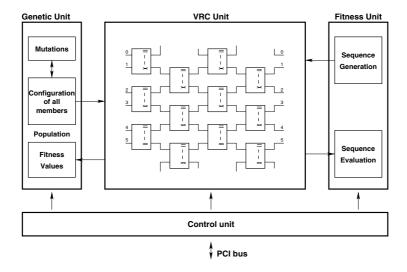

| A Flexible On-chip Evolution System Implemented on a Xilinx Virtex-II Pro Device  Kyrre Glette, Jim Torresen                                                    | 66 |

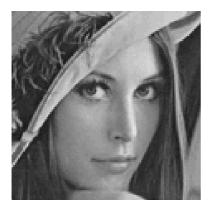

| An Evolvable Image Filter: Experimental Evaluation of a Complete Hardware Implementation in FPGA  Tomáš Martínek, Lukáš Sekanina                                | 76 |

| Evolution of Analog Circuits                                                                                                                                    |    |

| Operational Amplifiers: An Example for Multi-objective Optimization on an Analog Evolvable Hardware Platform  Martin Trefzer, Jörg Langeheine, Karlheinz Meier, |    |

86

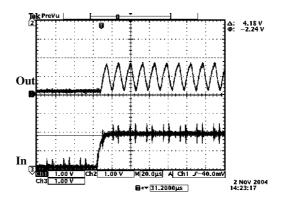

| Intrinsic Evolution of Controllable Oscillators in FPTA-2  Lukáš Sekanina, Ricardo S. Zebulum                                                                    | 98  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Evolutionary Robotics                                                                                                                                            |     |

| The Role of Non-linearity for Evolved Multifunctional Robot Behavior Martin Hülse, Steffen Wischmann, Frank Pasemann                                             | 108 |

| An On-the-fly Evolutionary Algorithm for Robot Motion Planning  Teddy Alfaro, María-Cristina Riff                                                                | 119 |

| Evolutionary Hardware Design Methodologies                                                                                                                       |     |

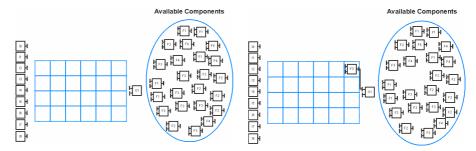

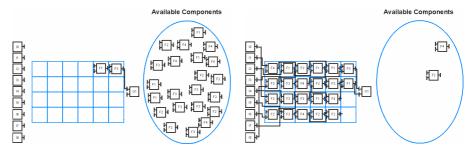

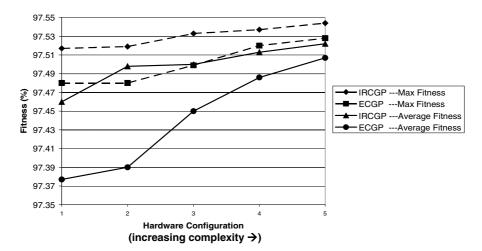

| Improving the Evolvability of Digital Multipliers Using Embedded Cartesian Genetic Programming and Product Reduction  James Alfred Walker, Julian Francis Miller | 131 |

| Benefits of Employing an Implicit Context Representation on Hardware Geometry of CGP  Xinye Cai, Stephen L. Smith, Andy M. Tyrrell                               | 143 |

| Evolution in Materio: Investigating the Stability of Robot Controllers Evolved in Liquid Crystal Simon Harding, Julian F. Miller                                 | 155 |

| Bio-inspired Architectures                                                                                                                                       |     |

| Hardware Implementation of 3D Self-replication  André Stauffer, Daniel Mange, Fabien Vannel                                                                      | 165 |

| POEtic: A Prototyping Platform for Bio-inspired Hardware  J. Manuel Moreno, Yann Thoma, Eduardo Sanchez                                                          | 177 |

| Implementation of Biologically Plausible Spiking Neural Networks Models on the POEtic Tissue                                                                     |     |

| J. Manuel Moreno, Jan Eriksson, Javier Iglesias, Alessandro E.P. Villa                                                                                           | 188 |

# Applications

| Adaptive Waveform Control in a Data Transceiver for Multi-speed |     |

|-----------------------------------------------------------------|-----|

| IEEE1394 and USB Communication                                  |     |

| Yuji Kasai, Eiichi Takahashi, Masaya Iwata, Yosuke Iijima,      |     |

| Hidenori Sakanashi, Masahiro Murakawa, Tetsuya Higuchi          | 198 |

| Evolution, Re-evolution, and Prototype of an X-Band Antenna for |     |

| NASA's Space Technology 5 Mission                               |     |

| Jason D. Lohn, Gregory S. Hornby, Derek S. Linden               | 205 |

| Hardware Platforms for MEMS Gyroscope Tuning Based on           |     |

| Evolutionary Computation Using Open-Loop and Closed-Loop        |     |

| Frequency Response                                              |     |

| Didier Keymeulen, Michael I. Ferguson, Wolfgang Fink,           |     |

| Boris Oks, Chris Peay, Richard Terrile, Yen-Cheng, Dennis Kim,  |     |

| Eric MacDonald, David Foor                                      | 215 |

|                                                                 |     |

| Author Index                                                    | 227 |

# **An Adaptive Self-tolerant Algorithm for Hardware Immune System**

Wenjian Luo, Xin Wang, Ying Tan, Yiguo Zhang, and Xufa Wang

Department of Computer Science and Technology,

University of Science and Technology of China, Hefei 230027, China

{wjluo, ytan, xfwang}@ustc.edu.cn

{sinbarwx, ygzhang}@mail.ustc.edu.cn

Abstract. Hardware immune systems have been studied with some initial achievements in recent years. Hardware immune systems are inspired by biological immune systems and they are expected to have many interesting characteristics, such as self-adaptive, self-learning and fault tolerant abilities. However, as novel intelligent systems, hardware immune systems are faced with many problems. This paper focuses on autoimmunization that is an inevitable problem when designing a complex hardware immune system. After the costimulation mechanism of biological immune system is simply introduced as a metaphor, a novel self-adaptive and self-tolerant algorithm for hardware immune systems is proposed in this paper. Inspired by the co-stimulation mechanism, the algorithm endows hardware immune systems with the capability of self-tolerance by automatically updating detector set and making the self set more complete. It can increase the accuracy of detection and decrease the rate of false positive effectively. Results of simulation experiments demonstrate the validity of this algorithm.

#### 1 Introduction

Many works have been devoted to computational methods that are inspired by biological immune system in recent years [1-2]. As novel computational methods of Computational Intelligence (CI), this kind of research is called as Artificial Immune Systems (AISs) or methods. Among the many works about AIS, the concept of hardware immune systems is a younger one, which is proposed as a novel approach to designing a kind of hardware system with the fault tolerant ability [3-4].

So far, some works about hardware immune system have already been done. The architecture of a hardware immune system is firstly discussed and studied by D. W. Bradley and A. M. Tyrrell [3]. Also, A. M. Tyrrell and his colleagues proposed the concept of Immunotronics, and tried to construct a new theory about the design of fault tolerant hardware [5-6]. Based on Embryonic Array, R. Canham and A. M. Tyrrell proposed a multi-layered hardware artificial immune system with learning ability, which used the fact that the immune system consists of acquired immune subsystem and innate immune subsystem for reference. The acquired layer of the immune system monitors the behaviors of system for unusual activities, and the non-learning innate layer is then employed to localize the fault if possible [7]. R. Canham and A. M. Tyrrell also developed a novel

artificial immune system, in which a detector of an immune system can be defined as a column in a 2-D feature space, and the generation and learning of detectors are fully automatic. It has been applied to robotics as an error detection system [8]. A. Tarakanov and D. Dasgupta proposed a novel architecture for building immunochips. The immunochip, by which information can be processed in a parallel and distributed manner, was evaluated with the problem of detecting dangerous ballistic situations in near-Earth space [9].

Generally, when the negative selection algorithm [10] is used to perform error detection in a complex fault tolerant hardware system, a complete set of self strings can not be obtained. Therefore, a part of matured detectors could become a threat to the system under monitoring because these detectors may match some unknown self strings. This problem is similar to the autoimmunization in biological immune system. For complex hardware systems, this problem seems inevitable, but there is no effective solution up to now.

Inspired by the co-stimulation mechanism which is used to maintain self-tolerance in biological immune systems, an adaptive self-tolerant algorithm for hardware immune system is proposed in this paper, it adopts Concurrent Error Detection (CED) technology [11] to provide the co-stimulation signal for the error detection system. It is named as ASTA-CED (the Adaptive Self-tolerant Algorithm with Concurrent Error Detection). The co-stimulation signal drives the error detection system to update the detector set automatically, delete detectors which bring autoimmune behaviors and generate new valid detectors. Therefore, ASTA-CED can avoid the occurrences of autoimmunization. Simulation experiments are carried out to show that this proposed algorithm can increase the accuracy of detection and decrease the ratio of false positives effectively.

The co-stimulation mechanism of biological immune system is simply discussed in section 2. Section 3 gives an introduction of the ASTA-CED in detail. Section 4 demonstrates the design of simulation experiments and the experimental results. And discussions are also given in section 4. Finally, section 5 is devoted to conclusions and future studies.

# 2 Immune Metaphor

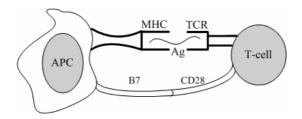

In the natural immune system, an inactive T-cell's activation needs not only the antigen recognition signal (the first signal), but also co-stimulation (the second signal) [12]. The source of the second signal can be various, mainly coming from the combination of B7 molecules on the surface of antigen presentation cells (APC) and CD28 molecules on the surface of T-cells. Although the second signal does not have specificity, without the second signal, a T-cell that has already obtained the first signal will become an anergy cell (which can not take its own responsibility), and even die. The activation process of a T-cell is presented in Fig. 1 [12].

Among many kinds of cells interacting with T-cells, only the professional APCs (playing a professional role of presenting a peptide of an antigen to T-cells and providing other corresponding signals) can provide the first and second signals to activate T-cells at the same time [12]. If a T-cell recognizes an antigen's peptide from

**Fig. 1.** This briefly shows that the activation of a T-cell should get the first and second signals. Here both first and second signals come from APC. However, the second signal, as a signal of co-stimulation, can come from various immune cells or molecules.

cells other than professional APCs, generally it will become an anergy cell because of the lack of the second signal. In fact, this is not likely to be a bad thing, because the antigen recognized is generally a self antigen at this time. In the biological immune system, new birth lymphocytes will undergo a maturation process, in which lymphocytes that bind with self proteins are destroyed. Hence, when released within the body, binding to a protein indicates it is non-self and may be a harmful pathogen. But the fact indicates that not all self proteins are presented to the maturing lymphocytes. This means some of the matured lymphocytes are still dangerous to the body. Thus, making the lymphocytes threatening the body become anergy cells or dies. This process is very helpful for the maintaining of self-tolerance [12].

Artificial hardware immune systems are presented with a similar problem, the current learning requires a period of fault free operation during which all the self states are presented. Although there are applications where this is possible, this can become a non-trivial task in some complex systems [7]. So, a mechanism to provide the second signals for artificial hardware immune systems is required.

# 3 ASTA-CED Algorithm

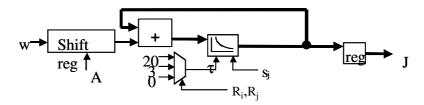

The negative selection algorithm is used for performing the detection of invalid state transitions. The negative selection algorithm, developed by Forrest and her colleagues [10, 13], is based on the generation process of T-Cells within the immune system. Forrest and her colleagues use a string to represent the self and non-self individuals. Partial matching between these self strings and non-self strings is used as a matching rule to distinguish between self and non-self. A set of detector strings are generated such that they do not match with all self strings, and they only match with non-self strings. Hence, the matching between a detector and the strings being protected gives an indication that some abnormal behaviors have occurred, and this indication is used as the first signal to the error detection system. In ASTA-CED algorithm, strings are used for representing the system's state transition but not just states because invalid state transitions can occur between valid states.

Concurrent Error Detection (CED) is widely used in highly dependable computing systems. It is a kind of on-line parity checking technology [11]. In the ASTA-CED algorithm, CED is used for performing parity checking on system's outputs and gen-

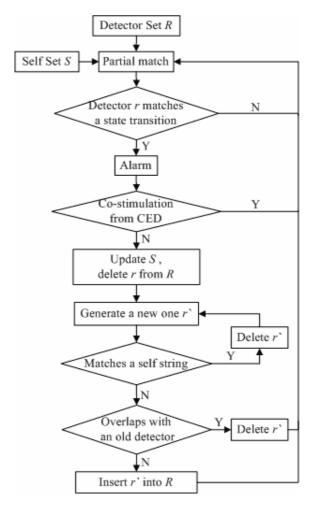

Fig. 2. This is the flow chart of ASTA-CED algorithm. The CED is used as a co-stimulation signal in ASTA-CED. Driven by this co-stimulation signal, the self set becomes more and more complete and the detector set evolves to be more and more efficient.

erating co-stimulation signals, because it is a simple and comparatively inexpensive technology to implement.

The ASTA-CED algorithm can be specified as shown in Fig. 2, in which S is the set of self (valid state transition) strings, and R is the set of detectors. The following is the description of the algorithm shown in Fig. 2. Here, it assumes that the initial set S is incomplete because a complete self set can not be obtained in general.

- (1) Perform partial matching between state transitions and detectors in R one by one;

- (2) If a detector r matches a state transition string, go to (3), or else back to (1);

- (3) Report the error, if there is no co-stimulation from CED, go to (4), or else back to (1);

- (4) Update the set *S* by inserting the new self string obtained by detector *r*, and delete *r* from *R*;

- (5) Generate a new premature detector r' randomly;

- (6) If r' doesn't match any string in S, go to (7), or delete it and back to (5);

- (7) If r' is included in the current set R, delete it, or else insert it into R;

- (8) Back to (1).

The aim of steps (5)-(8) is to generate a new detector and prevent the generating of new detectors from consuming too many resources of the system. The process of error detection can be regarded as the evolutionary process of the detector set R, by which the algorithm endows the hardware immune system with the capability of adaptive self-tolerance.

In the following experiments, every state transition of the whole string space appears once in a single cycle. When the detector set undergoes such a cycle, in fact it has evolved for one generation.

# 4 Experiments

#### 4.1 Design of the Experiments

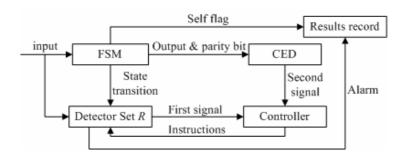

Based on the experiment of error detection of Finite State Machine (FSM) designed by A. M. Tyrrell [5], a co-stimulation generating module – CED and a controller are added to the simulation experiment, which is described as shown in Fig. 3. Partial matching of a state transition string from the FSM and a detector string from the detector set R will generate the first signal to the controller, and send an alarm to the results record module. At the same time, the self flag (which is set for every self string in S in advance) of the current state transition is sent to the results record module too. So the results recorded can be used for validating the performance of the ASTA-CED. In the CED module, the result of parity checking of the system's output will be sent to the controller as the second signal (co-stimulation), and then the controller decides whether R need to be updated according to the first and second signals. If necessary, R would be updated.

**Fig. 3.** This shows the design of the simulation experiment. In this experimental system, the CED is used to generate the second signal. The first and second signals are sent to the Controller Module that justify whether a matching result represented by the first signal is really an abnormal behavior or not. The final experimental results are stored in Results Record module.

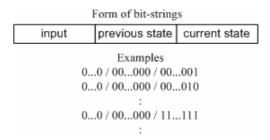

**Fig. 4.** This shows the bit-string representation of state transitions. Only previous state and current state are used because only the state transition is considered in this paper. The input state is ignored.

Here it supposes that valid state transitions generate valid outputs, and invalid state transitions generate invalid outputs, moreover, and every invalid output just fails at a single bit (here, the "invalid outputs" means outputs that fails to pass the parity checking). Bit-strings are used for representing state transitions and detectors in a form shown in Fig. 4 [4].

#### 4.2 Results

The ASTA-CED algorithm is compared with the traditional Negative Selection Algorithm (traditional NSA) which does not have a co-stimulation mechanism in the same situation. The length of the bit-string is 10, and then the size of string space O is 1024. The number of total self strings  $N_s$  is fixed at 60. The partial match length c is 8.

The parameter a, which is the proportion of self strings already known in advance among the complete set of self strings, is set to  $\{1.0, 0.9, 0.8, ..., 0.1\}$  for observing the change of the results against it.

Every state transition in space O appears for 40 times in an independent run of the algorithm. In other words, the detector set R in ASTA-CED algorithm will evolve for 40 generations in an independent run. And the results take the average values over 15 independent runs for every value of the parameter a.

The self set of every independent run is generated randomly. The size of initial immature detector set is fixed to 324. Both initial immature and mature detector sets of ASTA-CED are the same as that of traditional NSA. The size of initial mature detector set is  $N_{rl}$ , Table 1 lists the average values of  $N_{rl}$  against values of a.

It should be noted that the detector set of traditional NSA is fixed. However, the detector set of ASTA-CED will evolve step by step, and its evolution is driven by the co-stimulation signal (i.e. CED).

In an independent run, it is assumed that PS is the number of valid state transitions detected as normal behaviors by the system; FS is the number of valid state transitions detected as abnormal behaviors; PN is the number of invalid state transitions detected as normal behaviors; and FN is the number of invalid state transitions detected as abnormal behaviors. The following three statistical results are defined to make the comparisons between ASTA-CED and traditional NSA.

$$P_r = \frac{FN}{FS + FN}$$

,  $P_w = \frac{FS}{PS + FS}$ ,  $P_f = \frac{PN}{PN + FN}$

**Table 1.** The average sizes of initial mature detector sets of the two algorithms against values of *a*. The mature detector set is the detector set after being filtered out the immature detectors that matches self individuals from the immature detector set. The size of initial immature detector set is always set as 324.

| а                | 1.00  | 0.90  | 0.80  | 0.70  | 0.60  |

|------------------|-------|-------|-------|-------|-------|

| Average $N_{rl}$ | 195.5 | 206.5 | 220.0 | 225.0 | 240.5 |

| а                | 0.50  | 0.40  | 0.30  | 0.20  | 0.10  |

| Average $N_{rl}$ | 253.5 | 264.5 | 274.5 | 296.0 | 309.5 |

**Table 2.**  $P_r$  of traditional NSA and ASTA-CED

|      | Traditional | ASTA-CED            |                      |  |

|------|-------------|---------------------|----------------------|--|

| а    | NSA         | Average value from  | Average value from   |  |

|      |             | 1 to 20 generations | 21 to 40 generations |  |

| 1.00 | 1.0000      | 1.0000              | 1.0                  |  |

| 0.90 | 0.9934      | 0.9993              | 1.0                  |  |

| 0.80 | 0.9881      | 0.9989              | 1.0                  |  |

| 0.70 | 0.9816      | 0.9978              | 1.0                  |  |

| 0.60 | 0.9741      | 0.9969              | 1.0                  |  |

| 0.50 | 0.9698      | 0.9963              | 1.0                  |  |

| 0.40 | 0.9634      | 0.9953              | 1.0                  |  |

| 0.30 | 0.9586      | 0.9947              | 1.0                  |  |

| 0.20 | 0.9505      | 0.9936              | 1.0                  |  |

| 0.10 | 0.9466      | 0.9923              | 1.0                  |  |

**Table 3.**  $P_w$  of traditional NSA and ASTA-CED algorithms

|      | Traditional | ASTA-CED            |                      |  |

|------|-------------|---------------------|----------------------|--|

| a    | NSA         | Average value from  | Average value from   |  |

| NOA  |             | 1 to 20 generations | 21 to 40 generations |  |

| 1.00 | 0.0000      | 0.0000              | 0.0                  |  |

| 0.90 | 0.0814      | 0.0081              | 0.0                  |  |

| 0.80 | 0.1546      | 0.0138              | 0.0                  |  |

| 0.70 | 0.2441      | 0.0281              | 0.0                  |  |

| 0.60 | 0.3580      | 0.0407              | 0.0                  |  |

| 0.50 | 0.4231      | 0.0476              | 0.0                  |  |

| 0.40 | 0.5289      | 0.0635              | 0.0                  |  |

| 0.30 | 0.6103      | 0.0696              | 0.0                  |  |

| 0.20 | 0.7567      | 0.0838 0.0          |                      |  |

| 0.10 | 0.8381      | 0.1046              | 0.0                  |  |

|       | Traditional | ASTA-CED                               |                                         |  |

|-------|-------------|----------------------------------------|-----------------------------------------|--|

| a NSA |             | Average value from 1 to 20 generations | Average value from 21 to 40 generations |  |

| 1.00  | 0.2431      | 0.2431                                 | 0.2431                                  |  |

| 0.90  | 0.2218      | 0.2413                                 | 0.2421                                  |  |

| 0.80  | 0.1813      | 0.1970                                 | 0.1974                                  |  |

| 0.70  | 0.1714      | 0.1971                                 | 0.1990                                  |  |

| 0.60  | 0.1403      | 0.1771                                 | 0.1797                                  |  |

| 0.50  | 0.1319      | 0.1807                                 | 0.1839                                  |  |

| 0.40  | 0.1112      | 0.1443                                 | 0.1475                                  |  |

| 0.30  | 0.0982      | 0.1635                                 | 0.1673                                  |  |

| 0.20  | 0.0722      | 0.1729                                 | 0.1766                                  |  |

| 0.10  | 0.0514      | 0.1393                                 | 0.1449                                  |  |

**Table 4.**  $P_f$  of traditional NSA and ASTA-CED algorithms

Table 2, Table 3 and Table 4 show the comparison between ASTA-CED and traditional NSA on average values of  $P_r$ ,  $P_w$  and  $P_f$ . The comparisons in the first 20 generations, those are shown separately, indicate that on  $P_r$  and  $P_w$ , the results of ASTA-CED algorithm is much better than that of traditional NSA, this is due to the detectors matching self strings are deleted and new detectors are generated, and the  $P_r$  of the two algorithms increase with a, and both the  $P_w$  of them decrease as a increases; but only  $P_f$  of ASTA-CED algorithm is a little higher than that of traditional NSA, this will be discussed in the next section.

The comparisons in the last 20 generations are also shown separately in Table 2, 3 and 4. It is clear that in the last 20 generations, there is no detector matching a self string. In other words, the evolution of detector set R has been finished before these generations. For  $P_b$ , the results are similar to that of the first 20 generations.

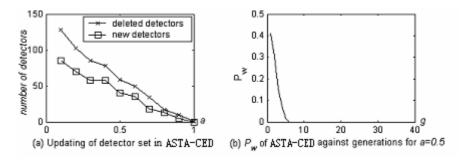

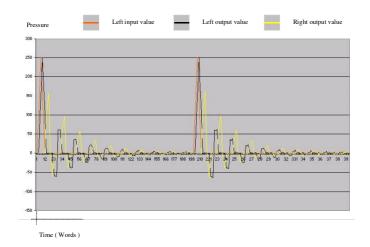

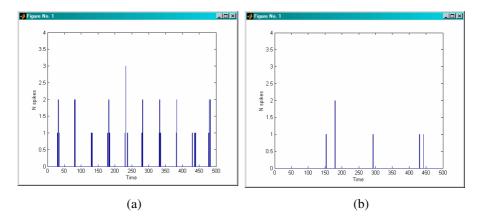

Some other aspects of ASTA-CED algorithm can be observed in Fig. 5. Firstly, in Fig. 5(a), it indicates that the number of new detectors inserted into R is smaller than

**Fig. 5.** This shows some characteristics of ASTA-CED. (a) The updating process of detector set R. (b) The changing curve of  $P_w$  in generations.

| а                | 1.00  | 0.90  | 0.80  | 0.70  | 0.60  |

|------------------|-------|-------|-------|-------|-------|

| Average $N_{r2}$ | 195.5 | 201.5 | 215.5 | 208.5 | 225.5 |

| а                | 0.50  | 0.40  | 0.30  | 0.20  | 0.10  |

| Average $N_{r2}$ | 235.0 | 244.0 | 246.5 | 263.0 | 266.5 |

Table 5. The average sizes of final detector sets of ASTA-CED against values of a

the number of deleted detector from R, this means that the size of R has shrunk in ASTA-CED algorithm. The size of final detector set of ASTA-CED is  $N_{r2}$ . Table 5 lists the average values of  $N_{r2}$  against values of a over 15 independent runs. On the other hand, in Fig. 5(b), the probability of false positive  $P_w$  declines rapidly to 0 against generations.

#### 4.3 Discussions

In Table 1, Table 2 and Table 3, the experimental results indicate that ASTA-CED algorithm is better than the traditional NSA both at  $P_r$  and  $P_w$ , but is poorer than traditional NSA at  $P_f$ . The following is a brief discussion about this phenomenon.

Since partial matching mechanism is being used here, even if a complete detector set can be obtained, the self strings and non-self strings matching over *c* contiguous bits will result in the presence of undetectable non-self strings, namely *holes* [13-14]. There are strings in the "hole" that are unable to be detected because any detectors matching them would also match some self strings. The relevant analyses of this phenomenon have been investigated by D'haeseleer in [14].

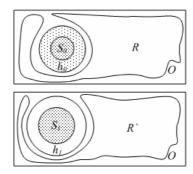

In Fig. 6, for a particular partial match length c, given  $S_0$  as the incomplete set of self got in advance and  $S_1$  as the more complete set of self obtained in the error detection procedure. Suppose  $h_0$  and  $h_1$  are the holes induced by  $S_0$  and  $S_1$  respectively, and R and R' are the detector sets generated against  $S_0$  and  $S_1$  respectively, and

**Fig. 6.** Analyses on failure probability  $P_f$ . O is the whole string space.  $S_0$  is the initial incomplete set of self, while  $S_1$  is the more complete set of self obtained in the course of error detection. R and R' are the detector sets generated against  $S_0$  and  $S_1$  respectively, while  $h_0$  and  $h_1$  are the holes induced by  $S_0$  and  $S_1$  respectively.

O is the whole string space. It is noted that here R and R' are regarded as complete or almost complete detector sets. This can be guaranteed by randomly generating enough premature detectors or using the greedy detector generating algorithms proposed in [13].

Firstly, it should be noted that  $S_0$  is a subset of  $S_I$ , because  $S_I$  is more complete than  $S_0$ . Strings in  $h_0$  can not be detected by R, and strings in  $h_1$  are undetectable to R'. Secondly, there can be self strings in the  $h_0$ , but no self string in the  $h_1$ . Suppose that all of self strings in  $h_0$  make up of a set of  $S_{h0}$ . Finally, according to the counting method of holes in [14],  $(h_0$ -  $S_{h0})$  is a subset of  $h_1$ . Therefore, on the one hand, nonself strings in  $h_1$  can not be detected by R', while possible to be detected by R. On the other hand, non-self strings in  $(h_0$ -  $S_{h0})$  can not be detected by R' and R. Thus, if  $P_{f0}$  is the failure probability of R, and  $P_{f1}$  is the failure probability of R', it can be concluded that  $P_{f0} < P_{f1}$ . Fortunately, the problem with holes can be avoided by adopting a matching rule with a variable matching length c [14].

#### 5 Conclusion

In the design of a complex hardware immune system, autoimmunization is an inevitable problem. In this paper, a novel self-adaptive algorithm, namely ASTA-CED, is proposed as a solution. Concurrent Error Detection (CED) technology is used for providing co-stimulation to the error detection system, and the detector set is updated automatically, then the occurrence of autoimmunization can be avoided. Results of simulation experiments prove that this new algorithm has increased the accuracy of detection and decreased the ratio of false positives effectively.

However, there are also some future works that should be studied to improve this algorithm. Firstly, CED is a technology based on parity checking, so it can only detect single bit fault. Secondly, since CED is used for checking the system's output in this paper, this might be unsuitable when considering some applications. We are looking for more suitable co-stimulation mechanisms, and we will explore better approaches to building up self-tolerance in hardware immune systems.

**Acknowledgement.** This work is supported by NSFC Foundation (No. 60404004), Nature Science Major Foundation from Anhui Education Bureau (No. 2004kj360zd) and Chinese Post-doc Science Foundation (No. 2003034433).

#### References

- [1] Castro, de L.N., Timmis, J.. Artificial Immune Systems: a New Computational Intelligence Approach. Springer-Verlag, London, (2002)

- [2] Dasgupta, D., Ji, Z, et al. Artificial Immune System(AIS) Research in the Last Five Years. Proceedings of the IEEE Congress on Evolutionary Computation (CEC'2003), Canberra, Australia, (2003) 123-130

- [3] Bradley, D.W., Tyrrell, A.M.. The Architecture For A Hardware Immune System. Proceedings of the 3rd NASA/dod Workshop on Evolvable Hardware, Long Beach, Cailfornia, July 12 14 (2001) 193-200

- [4] Bradley, D.W., Tyrrell A.M.. A Hardware Immune System for Benchmark State Machine Error Detection. Proceedings of the 2002 Congress on Evolutionary Computation, Honolulu, USA, (2002) 813-818

- [5] Bradley, D.W., Tyrrell A.M.. Immunotronics Novel Finite-State-Machine Architectures with Built-in Self-Test Using Self-Nonself Differentiation. IEEE Transactions on Evolutionary Computation, Vol.6, 3 (2002) 227-38

- [6] Tyrrell, A.M.. Computer know Thy self!: A Biological Way to Look at fault Tolerance. Proceedings of 2nd EuroMicro/IEEE Workshop Dependable Computing Systems, September, (1999) 129–135

- [7] Canham, R., Tyrrell, A.M.. A Learning, Multi-Layered, Hardware Artificial Immune System Implemented upon an Embryonic Array. Proceedings of 5th International Conference on Evolvable Systems, (2003) 174–185

- [8] Canham, R., Jackson, A.H., Tyrrell, A.M.. Robot Error Detection Using an Artificial Immune System. Proceedings of NASA/DoD Conference on Evolvable Hardware, July (2003) 199 – 207

- [9] Tarakanov, A., Dasgupta, D.. An Immunochip Architecture and its Emulation. Proceedings of NASA/DoD Conference on Evolvable Hardware, July 15-18 (2002) 261-265

- [10] Forrest, S., Perelson, A.S., Allen, L., Cherukuri, R.. Self-nonself Discrimination in a Computer. Proceedings of the 1994 IEEE Symposium on Research in Security and Privacy. Los Alamitos, CA: IEEE Computer Society Press, (1994) 202-212.

- [11] Chaohuang, Z., Saxena, N., McCluskey, E.J.. Finite State Machine Synthesis with Concurrent Error Detection. Proceedings of International Test Conference, Sept. 28-30 (1999) 672 679.

- [12] Guang-yan, Zhou. Principles of Immunology. Scientific and Technical Documents Publishing House, Shanghai (2000)

- [13] D'haeseleer, P., Forrest, S., Helman, P.. An Immunological Approach to Change Detection: Algorithms, Analysis and Implications. Proceedings of the IEEE Symposium on Security and Privacy, IEEE Computer Society Press (1996)

- [14] D'haeseleer, P.. Further Efficient Algorithms for Generating Antibody Strings. Department of Computer Science, University of New Mexico, Technical Report CS95-3 (1995)

# Consensus-Based Evaluation for Fault Isolation and On-line Evolutionary Regeneration

Kening Zhang, Ronald F. DeMara, and Carthik A. Sharma

Department of Electrical and Computer Engineering, University of Central Florida, Orlando, FL 32816-2450 demara@mail.ucf.edu

**Abstract.** While the fault repair capability of Evolvable Hardware (EH) approaches have been previously demonstrated, further improvements to fault handling capability can be achieved by exploiting population diversity during all phases of the fault handling process. A new paradigm for online EH regeneration using Genetic Algorithms (GAs) called Consensus Based Evaluation (CBE) is developed where the performance of individuals is assessed based on broad consensus of the population instead of a conventional fitness function. Adoption of CBE enables information contained in the population to not only enrich the evolutionary process, but also support fault detection and isolation. On-line regeneration of functionality is achieved without additional test vectors by using the results of competitions between individuals in the population. Relative fitness measures support adaptation of the fitness evaluation procedure to support graceful degredation even in the presence of unpredictable changes in the operational environment, inputs, or the FPGA application. Application of CBE to FPGA-based multipliers demonstrates 100% isolation of randomly injected stuckat faults and evolution of a complete regeneration within 135 repair iterations while precluding the propagation of any discrepant output. The throughput of the system is maintained at 85.35% throughout the repair process.

#### 1 Introduction

Evolutionary mechanisms can actively restore mission-critical functionality in SRAM-based reprogrammable devices such as *Field Programmable Gate Arrays* (FPGAs). They provide an alternative to device redundancy for dealing with permanent degradation due to radiation-induced stuck-at-faults, thermal fatigue, oxide breakdown, electromigration, and other local permanent damage without the increased weight and size normally associated with spares. Hence, recent research has focused on employing the capability for reconfiguration inherent in field programmable devices to increase reliability and autonomy [1], [2], [3], [4], [5]. In these experiments, fault-tolerance is evolved at design time, or achieved at repair-time using evolution after taking a detected failed unit offline. In both cases, GAs provided a population-based optimization algorithm with the objective of producing a single best-fit individual as the final product. They rely on a pre-determined static fitness function that does not consider an individual's utility relative to the rest of the

population. The evaluation mechanisms used in previous approaches depend on the application of exhaustive test vectors to determine the individual with the best response to all possible inputs. However, given that partially complete repairs are often the best attainable [4], [2], other individuals may outperform the best-fit individual over the range of inputs of interest. In particular, there is no guarantee that the individual with the best absolute fitness measure for an exhaustive set of test inputs will correspond to the individual within the population that has the best performance among individuals under the subset of inputs actually applied. Thus, exhaustive evaluation of regenerated alternatives is computationally expensive, yet not necessarily indicative of the optimal performing individual among a population of partially correct repairs. Hence, two innovations are developed herein for self-adaptive EH regeneration:

- 1) Elimination of additional test vectors, and

- 2) Temporal Assessment based on aging and outlier identification

In Consensus-based Evaluation (CBE), an initial population of functionally identical (same input-output behavior), yet physically distinct (alternative design or place-and-route realization) FPGA configurations is produced at design time. During runtime, these individuals compete for selection based on discrepancy favoring fault-free behavior. Discrepant behaviour, where the outputs of two competing individuals do not agree on a bit-by-bit basis, is used as the basis for the performance evaluation process. Any operationally visible fault will decrease the fitness of just those configurations that use it. Over a period of time, as the result of successive comparisons, a consensus emerges from the population regarding the relative fitness of all individuals. This allows the classification of configurations into ranges of relative reliabilities based on their observed performance during online operation.

#### 2 Related Work

Adaptive regeneration has been investigated as an alternative to using pre-determined spares. Most researchers [2], [3], [5], [6] focus on using traditional GAs to identify a single best-fit individual at the termination of the evolutionary computation. Keymeulen, Stoica, and Zebulum [1] use a design-time emphasis to improve fault tolerance. They develop evolutionary techniques so that a circuit is initially designed to remain functional even in presence of various faults. Their *population-based* fault tolerant design method evolves diverse circuits and then selects the most fault-insensitive individual. In this paper we propose a system that achieves improved fault tolerance by using a runtime adaptive algorithm that emphasizes the utilization of responses observed during the actual operation of the device. While their population-based fault tolerance approach provides passive run-time tolerance, CBE is dynamic and actively improves the fault tolerance of the system according to environmental demands.

Yao and Liu [7] emphasize that in evolutionary systems, the population contains more information than any one individual. They develop two examples to demonstrate the use of the information contained in the population in the domains of artificial neural networks and rule based systems respectively. The last population is

used efficiently and out-performs the single best-fit individual in these two examples. [8] presents four methods for combining the different individuals in the final population to generate the solution. They provide results for three data sets, namely the Australian credit card assessment problem, the heart disease problem and the diabetes problem, which show that solutions obtained by combining individuals outperform any single individual. While the authors devise a method to utilize the information contained in the population to improve the final solution, they fail to use the information in the population to improve the learning and optimization process itself. Also, the authors emphasize that learning systems are different from optimization problems, and that information contained in the population is only useful in learning systems. The proposed approach clearly indicates that even optimization and repair problems can benefit from population information. More recently, in [9] the authors describe using fitness sharing and negative correlation to create a diverse population of solutions. A combined solution is then obtained using a gating algorithm that ensures the best response to the observed stimuli. In EHW, it may not always be possible to combine solutions without additional physical resources that may be fault-prone. In our approach, all individuals in the population are recognized as possible solutions, with the best emerging candidate being selected based on their runtime response and performance track record. The authors also claim that applying the described techniques to EHW should be a straightforward matter, but do not describe any applications or examples. They state the absence of an optimal way of predicting the future performance of evolved circuits in unseen environments. We show that it is possible for an adaptive system to keep track of the relative performances of individuals and implicitly build a consensus.

Layzell and Thompson [10] identify Populational Fault Tolerance (PFT) as an inherent quality of EHW. They state that due to the incremental nature of evolutionary algorithms, the solution changes along the course of evolution to adapt to faults. The evolutionary history of the evolved circuit was used to arrive at the conclusion that PFT is an inherent quality in evolutionary design due to the incremental incorporation of additional components into a prototype depending on conditions. They speculate that PFT is less likely to occur for online evolution in varying environments. An evolutionary process that uses absolute fitness measures and exhaustive tests may not be able to provide adaptive fault tolerance.

Previous research has not focused on leveraging the robustness of a population to improve the detection and isolation phases, or to achieve an online evolution process. Problems related to fault tolerance in online evolution identified by the existing approaches are addressed by the new Consensus-based Evaluation scheme. Online evolution defines an essentially different problem from a traditional GA optimization problem. To address the problem effectively, a new fitness evaluation paradigm is required. With relative fitness measures based on competition, a running consensus is produced regarding the fitness of individuals in repsonse to the actual environmental stimuli. This can be used by the regeneration process to adapt to runtime requirements and improve the fault tolerance of the population. The CBE approach presents a new online adaptive repair mechanism that fully exploits the advantages of population-based evolutionary methods. It utilizes a *temporal voting* approach whereby the outputs of two competing instances are compared at any instant and alternative pairings are considered over time. The presence or absence of a discrepancy is used

to adjust the discrepancy values (DVs) of both individuals without rendering any judgment at that instant on which individual is actually faulty. The faulty, or later exonerated, configuration is determined over time through other pairings of competing configurations. The competitive process is applied repeatedly to form a strong consensus across the diverse pool of alternatives. The fitness of individuals is determined through this continuing runtime process by evaluating the real time performance of individuals in comparison to others in the population. Instead of using an absolute fitness function, with the concomitant exhaustive testing, relative discrepancy values are used as the threshold to identify faulty individuals. Also, the system actively selects individuals that perform the best, given the current environment. Healthy individuals are used to achieve the repair of individuals affected by faults. The proposed approach makes full use of the fact that repair complexity is far less than design complexity. CBE achieves improved fault tolerance by making extensive use of the information contained in the population – both as raw material for creating new individuals, and as information that enables faster and more accurate fault isolation. Any improvement in the fault isolation process speeds up the regeneration process by directing the GA search in the proper direction. The use of a relative fitness measure and temporal consensus improves the fault tolerance and adaptability of the population.

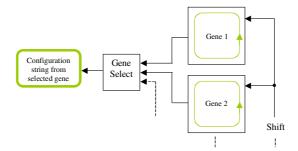

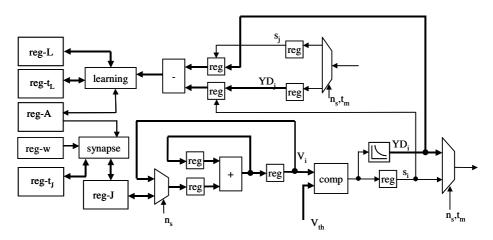

# 3 Autonomous Regeneration Using CBE

A GA performs a multi-directional search by maintaining a population of potential solutions and encouraging information formation and exchange along these directions. By encouraging direct competition between individuals in the population, a relative fitness measure based on consensus can be generated. The objective fitness function used in traditional GAs can be effectively replaced by the emergent consensus and relative fitness measure. The relative fitness measure is inherently dynamic, and by using an *Evaluation Window* for the individuals, an accurate reflection of the environmental conditions and changes can be achieved. Multiple potential directions for future exploration can be created and utilized depending on the conditions prevalent during the evolutionary process.

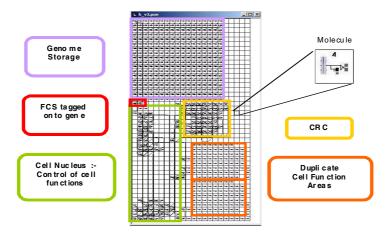

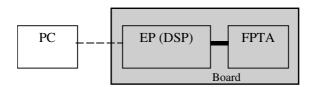

In the CBE approach, an initial population of *Pristine* individuals is created by manual design. These primordial configurations are functionally-identical (same input-output behavior), yet they utilize physically-distinct resources (alternative design or place-and-route implementations). For puposes of illustration, assume two competing *half-configurations* labeled Functional Logic Left ("L") and Functional Logic Right ("R") are loaded in tandem on the physical FPGA platform. The half-configurations occupy mutually exclusive physical resources to implement identical functionality. This realizes a conventional Concurrent Error Detection (CED) arrangement to identify at least any single resource fault with certainty [11]. As in traditional CED approaches, comparison of the outputs of the two resident half-configurations will produce either *discrepant* or *matching* outputs which will indicate the presence or absence of faulty resources in the FPGA hardware platform respectively.

Under CBE, whenever two half-configurations disagree, the *Discrepancy Value* (DV) of both half-configurations are incremented. By repeated pairing over a period of time, only those half-configurations which do not use faulty resources will eventually become preferred. This is because the DV of a faulty half-configuration is always increased regardless of its pairing, yet the DV of fault-free half-configurations which are paired together do not increase. This process occurs as part of the normal processing throughput of the FPGA without additional test vectors or other diagnostic routines. The determination of a configuration's health state is based on its cumulative DV relative to DV of the other individuals in the population evaluated over a period called the *Evaluation Window*, denoted by  $E^W$ .

#### 3.1 CBE Procedure

The procedure begins with pre-designed individuals that are fault-free. These individuals are divided into two groups, L and R, where each group of individuals uses mutually exclusive physical resources. This is essential to ensure that one individual each form both groups can reside and compete in tandem on the FPGA. In addition, every individual can belong to one of four states – Pristine, Suspect, Under-repair or Refurbished. In the beginning, all individual are pristine. At any given point of time, one individual each from the L and R groups compete with each other. State transistions occur according to the result of pairwise output comparison. A comparison can lead to two results - "L=R" and " $L\neq R$ " indicating whether the two resident half-configurations produce either matching or discrepant outputs, respectively. When L=R occurs then both individuals retain their Pristine state. However when their outputs disagree then both the configurations are demoted to the Suspect pool and the DV of both individuals is increased. Whenever such a transition occurs, a Fault Alert indicator is issued because two functionally-identical circuits disagree. Hence at least one resource fault must have occurred.

More formally, the *i*-th half configuration remains in the *Suspect* pool until its DV  $f_i$  evaluated over the preceding  $E^W$  pairings rises above the *Repair Discrepancy Value*  $(f_i < DV_R)$  which is defined as average DV of entire population accumulated over  $E^W$ . The *i*-th half-configuration is then marked as *Under Repair* until its DV drops below the *Operational Discrepancy Value*  $(f_i \ge DV_O)$  which is defined as average DV of the healthy individuals among the population (*Pristine, Suspect and Refurbished*) accumulated over  $E^W$ . Under the fault-free circumstance, DV<sub>O</sub> =  $DV_R$  until the faulty individuals appear in the population as a result of emergent hardware faults. Thereafter,  $f_{OT}$  is modified such that DV<sub>O</sub>  $\le DV_R$  which provides dithering immunity such that the configuration is indeed *Refurbished*.

Over a period of time the DV of an individual could increase further and *complete regeneration* becomes possible though not necessarily externally distinguishable from *partial regeneration*. Competing half-configurations remain *Refurbished* unless their DV rises above the Repair DV, at which time they again demoted to the *Under Repair* state.

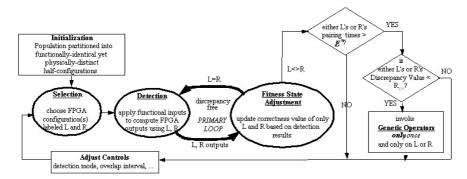

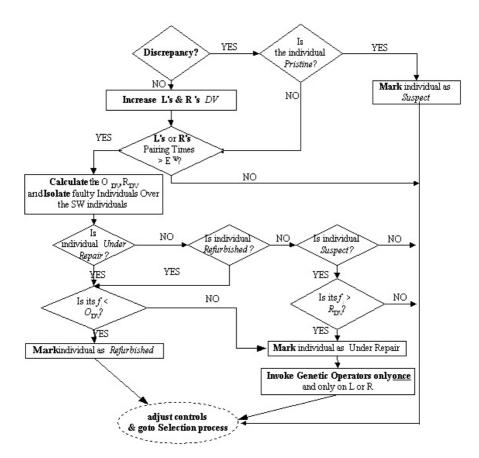

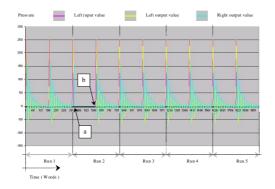

The procedural flow of the CBE algorithm that calculates the health state transitions is depicted in Figure 1. After initialization, *Selection* of the *L* and *R* half-configurations occurs which are then loaded into the FPGA. The *Detection* process is

**Fig. 1.** Procedural Flow in the CBE Technique

conducted when the normal data processing inputs are applied to the FPGA. Based on agreement or disagreement among the outputs of the two competing L and R half-configurations, Discrepancy Value Adjustment for both individuals occurs. The central PRIMARY LOOP representing discrepancy-free behavior can repeat indefinitely without any reconfiguration of the FPGA. Only when outputs disagree do alternate configurations need to be loaded. For Under Repair individuals, if  $f_i > DV_R$  then Genetic Operators are invoked only once on the resident configurations. The modified configuration is then immediately returned to the pool of competing configurations and the Selection step is resumed under normal FPGA throughput processing operations.

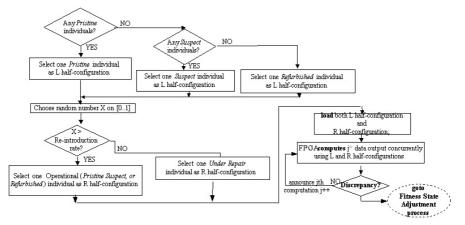

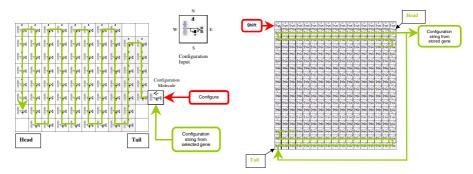

#### 3.2 Selection and Detection Process

The Selection and Detection processes are shown in Figure 2. The usual flow is for Pristine, Suspect, and then Refurbished individuals to be preferred in that order for one half-configuration. On the other hand, the other half-configuration is selected based on a stochastic process determined by the Re-introduction Rate ( $\lambda_R$ ). In particular, Under Repair individuals are selected as one of the competing half-configurations on average at a rate equal to  $\lambda_R$ . Henceforth, this now genetically-modified configuration will be re-introduced into the operational throughput flow as a new competitor to potentially exhibit fault-free behavior against the larger pool of configurations not currently undergoing repair.

An additional innovation is that  $\lambda_R$  is not only a continuous variable, but can be adapted under autonomous control. In particular, we strive for Mean-Time-To-Repair (MTTR) < Mean-Time-Between-Failures (MTBF) by monitoring the ratio of the number of computations elapsed between and adjusting  $\lambda_R$  accordingly.

The Detection process is presented in the lower right corner of Figure 2. If a discrepancy is observed as a result of output comparison, the FPGA is reconfigured with a different pair of competing configurations and the output of the device is temporarily held to be recalculated by the newly selected L and R half-configurations. These repeated computations and comparisons imply no additional cost since the device remains online and operational and the normal data throughput continues uninterrupted.

Fig. 2. Selection and Detection in the CBE Technique

Fig. 3. Fitness State Adjustment Processes in the CBE Technique

#### 3.3 Fitness State Adjustment Process

Figure 3 depicts the *Fitness State Adjustment Process* in CBE. Whenever a discrepancy is detected, the discrepancy values of the individuals involved are updated. The new discrepancy values are then compared to the *Repair Discrepancy Value DV<sub>R</sub>* and *Operational Discrepancy Value DV<sub>O</sub>* to determine whether the individuals move from one fitness state to another. Ideally, the repair and operational discrepancy values are computed over  $E^W$  comparisons for the population. As soon as the all the individuals in the population have completed at least  $E^W$  comparisons, new values of these thresholds are obtained. Since it may be impractical to wait for all individuals to complete the requisite iterations, an individual can undergo a state transition after it finishes  $E^W$  iterations. A *Sliding window* is defined, which reduces the latency involved in updating  $DV_R$  and  $DV_O$  by considering a subset of individuals instead of the whole population. With a sliding window, the values of these thresholds are updated upon the completion of the requisite number of iterations by the number of individuals defined by the sliding window. For *Under Repair* individuals, GA operators are invoked once every  $E^W$  iterations.

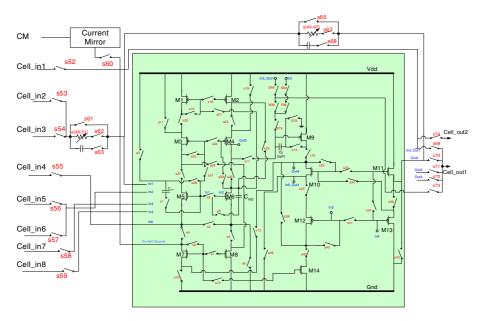

# 4 Evolutionary Fault Repair Circuit

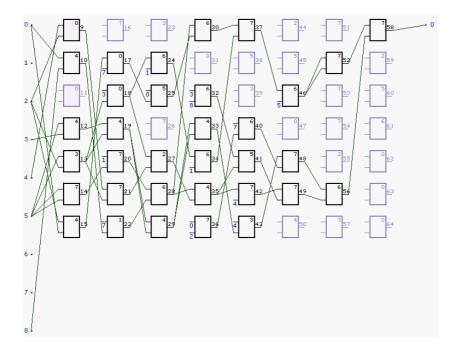

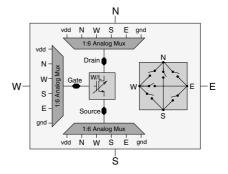

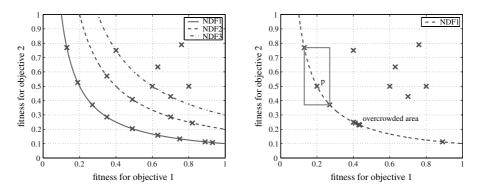

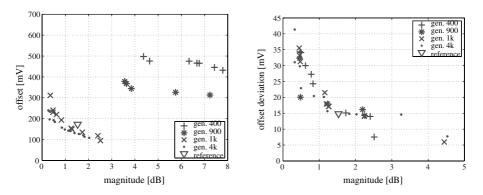

The hypothetical FPGA structure used in the CBE approach is the same as that in Miller, Thomson[12]. The feed-forward combinational logic digital circuit uses a rectangular array of nodes with two inputs and one output. Each node represents a Look-up Table (LUT) in the FGPA device, and a Configurable Logic Block (CLB) is composed of four LUTs. In the array, each CLB will be a row of the array and two LUTs are represented as four columns of the array. There are five dyadic functions --OR, AND, XOR, NOR, NAND -- and one unary-function NOT, each of which can be assigned to an LUT. The LUTs in the CLB array are indexed from 1 to *n*. Array routing is defined by the internal connectivity and the inputs/outputs of the array. Internal connectivity is specified by the connections between the array cells. The inputs of the cells can only be the outputs of cells with lower row numbers. Thus, the linear labelling and connection restrictions impose a feed-forward structure on the combinational circuit.

A 3×3 Multiplier is implemented using the above FPGA structure. XOR gates are purposely excluded from the initial designs which leads to designs with a higher number of the gates than conventional 3×3 Multiplier designs to increase the design space. The entire configuration needs 21 CLBs. The population of competing alternatives is then divided into two groups, *L* and *R*, where each group uses an exclusive set of physical resources. For crossover to occur such that offspring are guaranteed to utilize only mutually-exclusive physical resources with other resident half-configurations, a two-point crossover operation is carried out with another randomly selected *Pristine*, *Suspect* or *Refurbished* individual belonging to the same group. By enforcing speciation breeding occurs exclusively in *L* or *R*, and non-interfering resource use is maintained. The random crossover points are chosen along the boundary of CLBs so that intra-CLB crossover is not possible. The mutation

operator randomly changes the LUT's functionality or reconnects one input of the LUT to a new randomly selected output inside the CLB.

# **5** Experimental Results

An initial population of 20 fault-free configurations was partitioned into mutually exclusive sub-populations L and R, each containing 10 configurations. Varying stuckat faults were injected into the architecture that represents permanent physical faults. Several fault isolation and regeneration experiments were carried out using a software simulator. The  $E^W$  used in the experiment is 600, which can statistically guarantee that all of 64 input combinations appear at the inputs at least once with probablity of 99.5%, when input combinations are selected at random. For the  $3\times3$  multiplier, the total possible number of input combinations is  $2^6$ =64. Thus n = 64 represents the total number of unique input combinations to the simulated FPGA. In the simulation, m ( $0 \le m \le 64$ ) is defined as the number of input combinations for which a fault is manifested at the output of the simulated circuit. The number of input combinations for which the output does not match the desired value measures the impact of a fault on an individual. Fault isolation characteristics are analyzed first without considering the regeneration process.

The second set of regenerative experiments investigates the regeneration of functionality using CBE. The GA uses a two-point crossover, with a crossover rate of 0.05 and the mutation rate is 0.8. The re-introduction rate is 10%. With the simulated FPGA remaining partially online, all of the regeneration experiments achieved full fault recovery within a few hundred repair operations with normal functional data input. During the regeneration period, data throughput is average 87.94. That is, only 13.16% of the total computations had to be recalculated in order to preclude propagation of discrepant outputs.

#### **5.1** Fault Isolation Experiments

Pairs of individuals, one each from the L and the R groups are loaded on the FPGA in a repetitive random process. The outputs are compared to check for discrepancies. Judgment on the fault characteristics of an individual is reserved till it completes  $E^W$  pairings, and an *Observation Interval* is complete. A *Sliding Window* of evaluation is defined as five  $E^W$ , after which one observation interval is complete and individuals who have completed an  $E^W$  are evaluated to identify outliers. The DV of a faulty configuration will increase each time it is compared to another individual. A fault-free individual will see increases in its DV only when it is compared to a faulty individual. Individuals with a DV that exceeds the observed arithmetic mean by one standard deviation are identified as faulty. For example, if 1-out-of-64 outputs are affected in one L individual due to a fault, the expected DV of this individual after  $E^W$  pairings is  $DV_L = 1/64*E^W = 9.375$ , assuming equal likelihoods for inputs. A faulty individual can be expected to be identified once every two observation intervals, since the width of each observation interval is defined by  $5*E^W$ . The average DV of the R individuals that this is paired with be  $DV_R = 1/64*E^W$  /10=0.9375, assuming equal selection likelihoods.

Two metrics *Operational DV* ( $DV_O$ ) and *Repair DV* ( $DV_R$ ) are calculated and used in the CBA evaluation.  $DV_O$  is defined as arithmetic mean of the observed DV of all healthy individuals over a sliding winodw and the  $DV_R$  is defined as arithmetic mean of the DV of all individuals considered in the sliding window, including any that may be faulty. If no faulty individuals have been detected,  $DV_O$  will equal  $DV_R$ , otherwise the  $DV_O < DV_R$  as the faulty individuals substantially increase the mean DV.  $DV_O$  and  $DV_R$  are subsequently used in the CBE fault repair mechanism to define the state transitions of individuals. If an individual has a  $DV < DV_O$ , it is probably fault-free and can be used for fault-free computation. If the DV of an individual exceeds  $DV_R$ , then the individual is placed in the *Under-Repair* group.

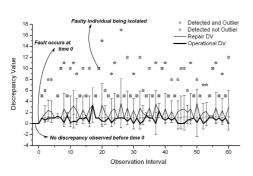

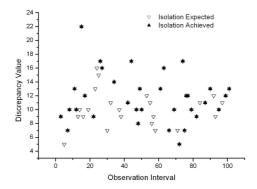

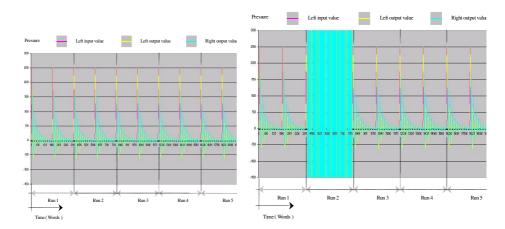

In the first experiment, only one individual is affected by a failure in the physical resource, which causes a 1-out-of-64 fault in the individual. Before the fault occurs, the system operates with a 100% throughput, and all individuals have a DV equal to zero. As shown in Figure 4, the fault occurs at time t=0 and the faulty individual is repeatedly detected and identified at various observation intervals.  $DV_O = DV_R$  whenever no faulty individual have been detected over a sliding window. The faulty individual is always detected, but since it has not completed  $E^W$  pairing, judgment is reserved, as shown in the plot. When a faulty individual is isolated, the  $DV_O$  will be less than  $DV_R$  and the faulty DV will be located outside of the  $DV_R + DV_O$  where  $DV_O$  represents the standard deviation of the discrepancy values.

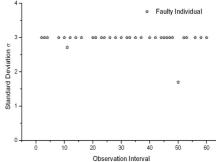

Figure 5 shows that the isolated individual's DV deviates by  $1\sigma$  or more, typically  $3\sigma$ . This shows error-free isolation and that faults are never incorrectly identified. Also, 100% of the faulty individuals are identified within statistically acceptable values for their discrepancies.

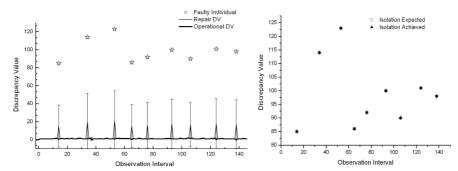

The average DV of individuals will increase proportionately with fault impact. This leads to increased isolation latency, as shown in Figure 6, for the second experiment, where the characteristics of isolating a single faulty individual with a 10-out-of-64 fault impact are shown. Since there are more faults, the faulty individual is expected to show a discrepancy (10/64)\*600 = 93.75 times over its evaluation window. To complete these iterations, it will therefore require (93.75/5) = 18.75 observation intervals, as opposed to 1.88 previously, which leads to both increased discrepancy values for the isolated individuals and an increased time between

**Fig. 4.** Isolation of a single faulty L individual with a 1-out-of-64 fault impact

**Fig. 5.** Plot of Standard Deviations of DV with a 1-out-of-64 fault impact

**Fig. 6.** Isolation of a single faulty L individual with a 10-out-of-64 fault impact

**Fig. 7.** Performance with a single faulty individual with 10-out-of-64 fault impact

successive isolations as compared to Figure 4. The detection latency remains unaffected. Figure 7 shows that for a single faulty L individual, with a *10-out-of-64* fault impact, isolation always succeeds when expected.

However, when more than one individual is affected by a resource fault, isolation is more time-consuming and difficult as shown in Figure 8, which depicts the isolation characteristics when 4 L and 4 R individuals are affected by I-out-of-64 faults. Expected isolations do not occur approximately 40% of the time, as the average discrepancy value of the population is higher, making outlier isolation difficult. The faulty individuals are always detected, but the higher number of discrepancies prevents them from completing  $E^W$  iterations within an observation interval. However, a fault-free individual is never incorrectly identified as being faulty.

Fig. 8. Isolation of 8 faulty individuals, 4 L and 4 R, each with a 1-out-of-64 fault impact

#### 5.2 Regeneration of Functionality

CBE-based regeneration experiments were performed on a simulated FPGA platform for the 3x3 multiplier application. Starting with an initial population of 20 viable configurations, random stuck-at faults were injected randomly into one of the 21

CLBs that were utilized to implement the multiplier. The fault reduced the number of correct outputs from 64-out-of-64 to 54-out-of-64. Regeneration was performed using a fitness-state adjustment process that utilized the results of the isolation process described in previous sections. A re-introduction rate of 10% was selected for selecting individuals under repair for performance evaluation. Higher re-introduction rates would lower the throughput whereas if the re-introduction rate is too low, the repair process will be unduly slowed down due to the decreased opportunities to evaluate the performance of the individuals under repair. A low crossover rate of 0.05 was used to ensure that the diversity in the population is preserved. The initial seeding population consists entirely of diverse hand-designed individuals. The mutation rate of 0.8 is required to ensure that the algorithm can explore alternatives by changing the logical functionality of LUTs and the interconnections between them.

While the simulated FPGA remained partially online, regeneration improved correctness to 64-out-of-64 possible outputs. Including iterations that produced functional outputs, the process concluded after a total of 218076 iterations. Complete repair was achieved after only 135 repair iterations when starting with a highly diverse initial population. The fault-affected individual was loaded on the FPGA for a total of 31636 iterations. During the regeneration period, data throughput was 85.54%. Hence, only 14.46% of the total computations needed to be redundant in order to preclude propagation of any discrepant outputs, even when candidate repairs were being re-introduced to refurbish the impacted FPGA configuration without additional test vectors. The throughput will be significantly higher when the system starts from a fault-free situation, since a large number of the initial iterations before the occurrence of the fault will contribute to improving the throughput. Fault isolation using consensus-based evaluation improved the performance of the repair process eliminating the use of an absolute fitness function. The diversity of the initial population provides for increased fault tolerance and also the raw material for realizing the repair.

#### 6 Conclusion

Online EH regeneration essentially defines a problem that is different from offline EH design. CBE leverages the fact that a failed system's *Repair Complexity* can often be much more computationally tractable than either its original *Design Complexity* or its *Re-Design Complexity*, both of which operate in the absence of a diverse population of previously completely correct alternatives. In particular, "repair" implies working design(s) being available before the occurrence of a resource failure. A population of working designs can thus facilitate repair by providing diverse alternates. Conventional fitness evaluation associates a rigid *individual-centric* fitness measure defined at design-time. CBE uses instead, a self-adapting *population-centric* assessment method at run-time. Population-centric assessment methods such as CBE can provide an additional degree of adaptability and autonomy. Finally, an additional benefit of CBE is that fitness evaluation becomes independent of the application running on the FPGA enabling *model-free* assessment during evolutionary repair.

# Acknowledgments

This research was supported in part by NASA Intelligent Systems NRA Contract NNA04CL07A.

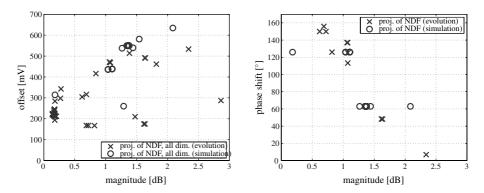

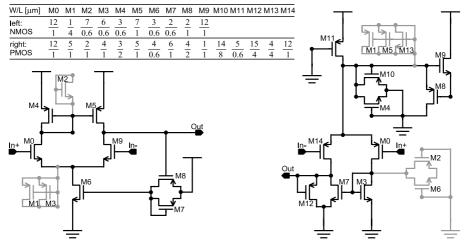

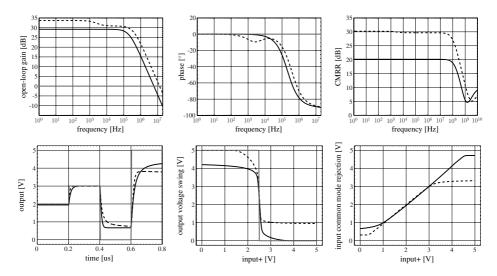

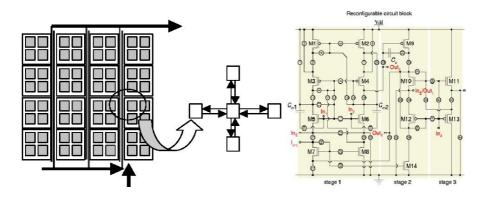

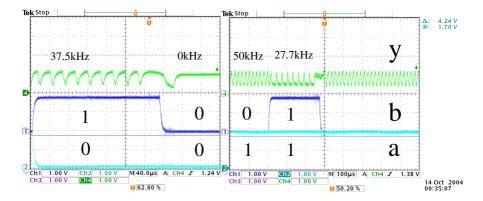

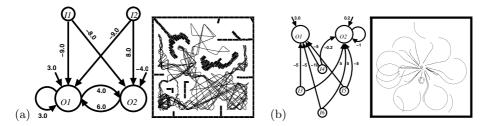

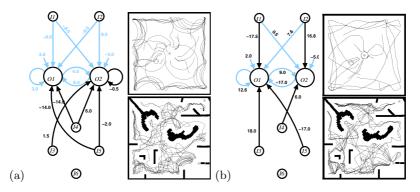

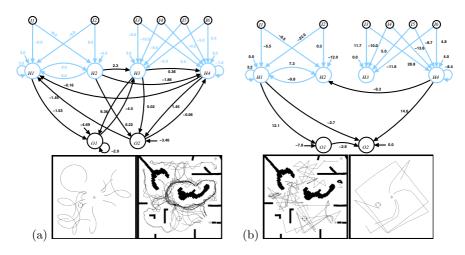

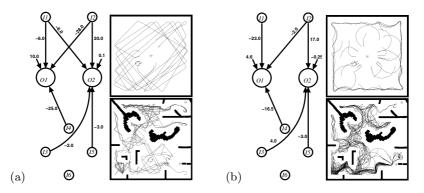

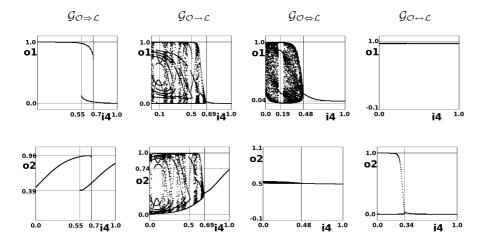

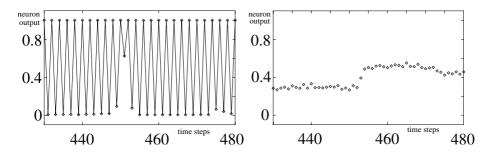

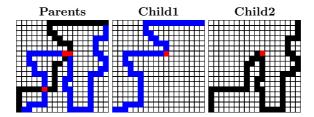

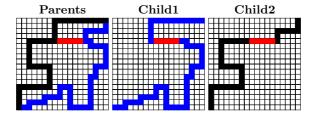

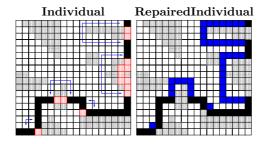

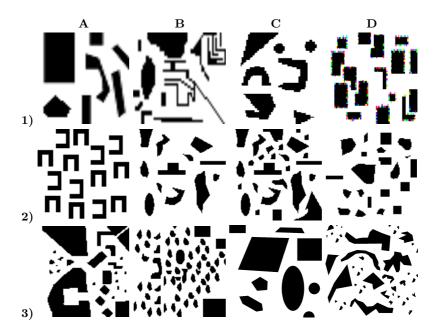

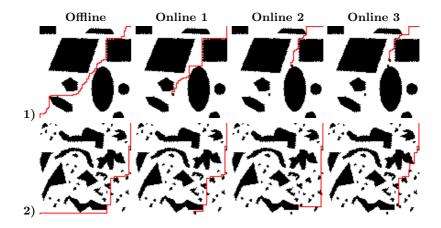

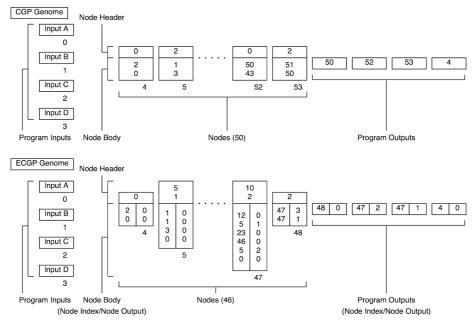

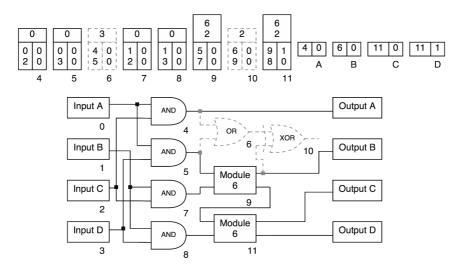

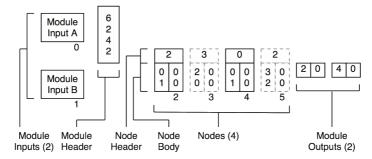

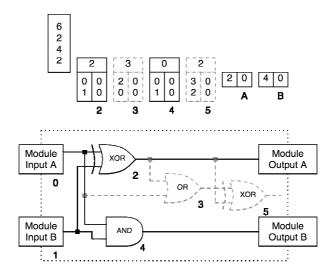

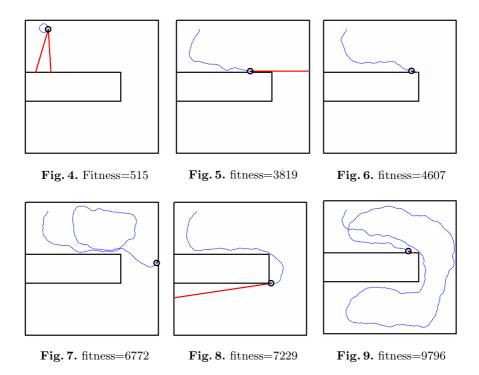

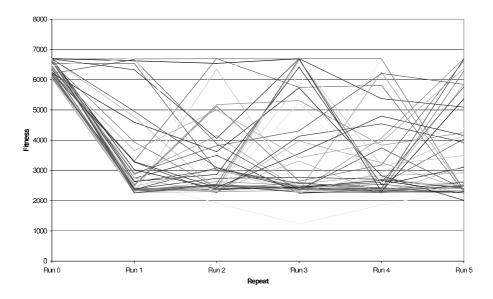

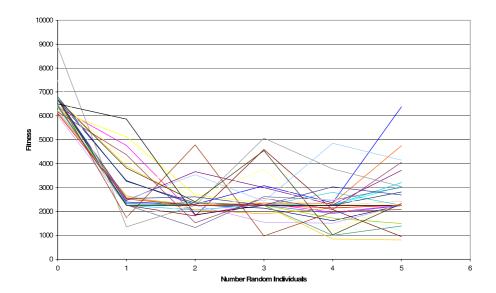

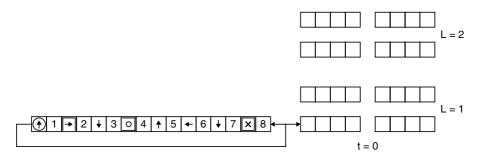

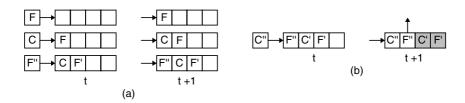

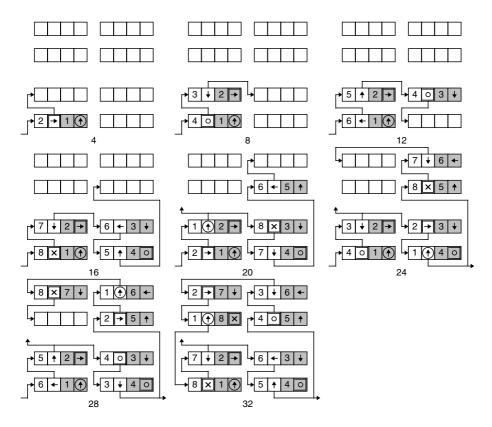

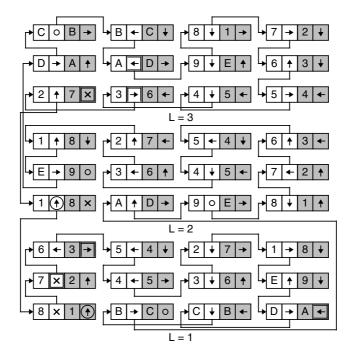

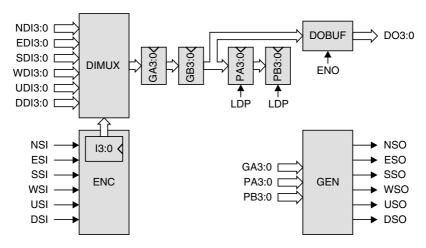

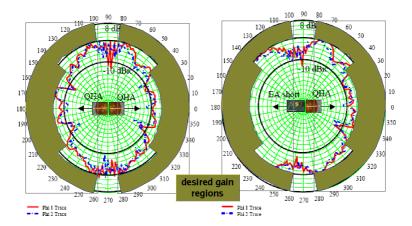

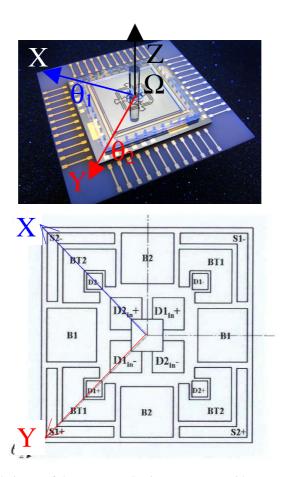

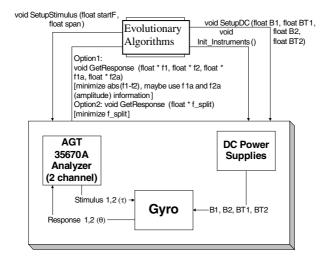

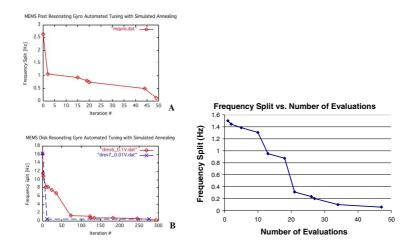

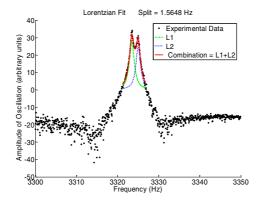

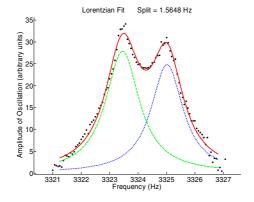

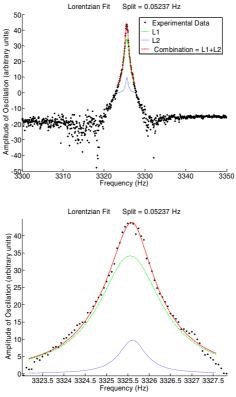

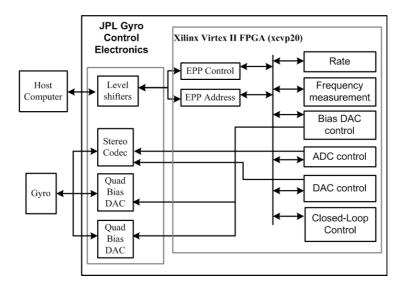

#### References